实验目的

实验任务

本实验的任务是描述一个RS触发器电路,并通过STEP FPGA开发板的12MHz晶振作为触发器时钟信号clk,拨码开关的状态作为触发器输入信号S,R,触发器的输出信号Q和非Q,用来分别驱动开发板上的LED,在clk上升沿的驱动下,当拨码开关状态变化时LED状态发生相应变化。

实验原理

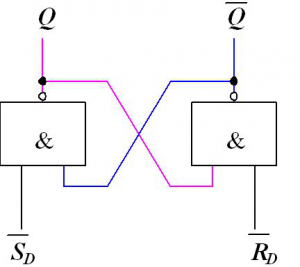

基本RS触发器可以由两个与非门按正反馈方式闭合构成。通常将Q端的状态定义为锁存器的状态,即Q=1时,称为锁存器处于1的状态;Q=0时,称锁存器处于0的状态,电路具有两个稳态。电路要改变状态必须加入触发信号,因是与非门构成的基本RS触发器,所以,触发信号是低电平有效。非Rd和非Sd是一次信号,只能一个个加,即它们不能同时为低电平,因为会有逻辑矛盾(Q == 非Q)。

Verilog HDL建模描述

用数据流描述实现的RS触发器程序清单rsff.v module rsff

( inputwireclk,r,s, //rs触发器输入信号 outputregq, //输出端口q,在always块里赋值,定义为reg型 outputwireqb //输出端口非q ); assignqb=~q; always@(posedgeclk) begin case({r,s}) 2'b00:q<=q;//r,s同时为低电平,触发器保持状态不变 2'b01:q<=1'b1; //触发器置1状态 2'b10:q<=1'b0;//触发器置0状态 2'b11:q<=1'bx;//r,s同时为高电平有效,逻辑矛盾,触发器为不定态 endcase end endmodule

仿真文件rsfftb.v

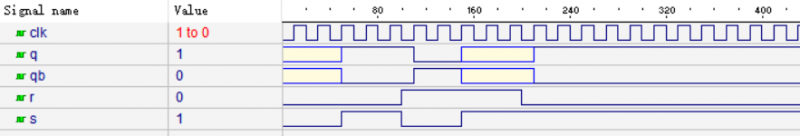

`timescale1ns/100ps//仿真时间单位/时间精度 modulers_ff_tb(); regclk,r,s; //需要产生的激励信号定义 wireq,qb; //需要观察的输出信号定义 //初始化过程块 initial begin clk=0; r=0; s=0; #50 r=0; s=1; #50 r=1; s=0; #50 r=1; s=1; #50 r=0; s=1; end always#10clk=~clk;//产生输入clk,频率50MHz //module调用例化格式 rs_ffu1(//rs_ff表示所要例化的module名称,u1是我们定义的例化名称 .clk(clk),//输入输出信号连接。 .r(r), .s(s), .q(q),//输出信号连接 .qb(qb) ); endmodule