硬件说明

蜂鸣器的分类:按其结构主要分为压电式蜂鸣器和电磁式蜂鸣器两种类型:

按是否带有信号源分为有源蜂鸣器和无源蜂鸣器两种类型:

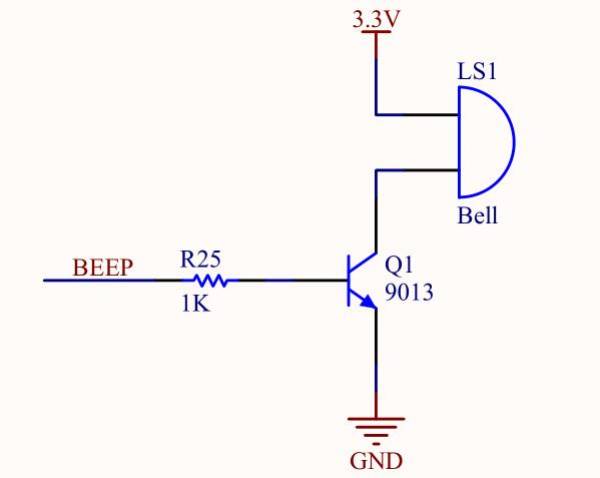

本章节和大家一起学习无源蜂鸣器的驱动,FPGA或单片机的GPIO口驱动能力弱,不能直接驱动无源蜂鸣器,常用的蜂鸣器驱动电路如下:

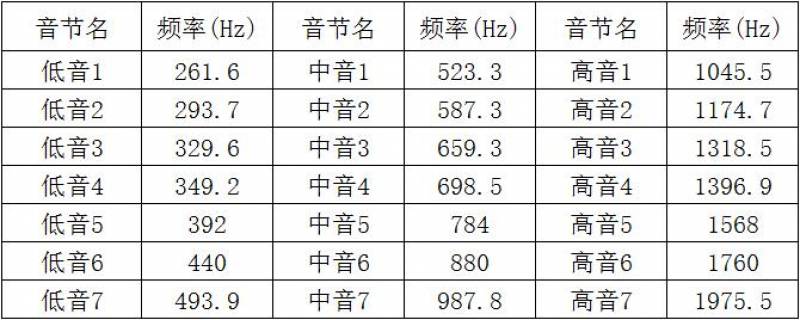

蜂鸣器使用NPN三极管(9013)驱动,三极管当开关用,当基极电压拉高时,蜂鸣器通电,当基极电压拉低时,蜂鸣器断电,FPGA控制GPIO口给三极管的基极输出不同频率的脉冲信号,蜂鸣器就可以发出不同的音节。不同音节与蜂鸣器震荡频率的对应关系如下:

我们使用PWM的方法(关于PWM的说明,快速入门中的脉冲发生器章节有详细的介绍),使用计数器对系统时钟进行分频,改变计数器的计数终值从而实现调节PWM信号频率的目的,使用PWM信号控制蜂鸣器电路。

Verilog代码

//-------------------------------------------------------------------- //>>>>>>>>>>>>>>>>>>>>>>>>>COPYRIGHTNOTICE<<<<<<<<<<<<<<<<<<<<<<<<< //-------------------------------------------------------------------- //Module:Beeper // //Author:Step // //Description:Beeper //-------------------------------------------------------------------- //CodeRevisionHistory: //-------------------------------------------------------------------- //Version:|Mod.Date:|ChangesMade: //V1.0|2016/04/20|Initialver //-------------------------------------------------------------------- moduleBeeper ( input clk_in, //系统时钟 input rst_n_in, //系统复位,低有效 input tone_en, //蜂鸣器使能信号 input [4:0] tone, //蜂鸣器音节控制 output reg piano_out //蜂鸣器控制输出) ; /* 无源蜂鸣器可以发出不同的音节,与蜂鸣器震动的频率(等于蜂鸣器控制信号的频率)相关, 为了让蜂鸣器控制信号产生不同的频率,我们使用计数器计数(分频)实现,不同的音节控制对应不同的计数终值(分频系数) 计数器根据计数终值计数并分频,产生蜂鸣器控制信号 */ reg[15:0]time_end;//根据不同的音节控制,选择对应的计数终值(分频系数) //低音1的频率为261.6Hz,蜂鸣器控制信号周期应为12MHz/261.6Hz=45871.5, //因为本设计中蜂鸣器控制信号是按计数器周期翻转的,所以几种终值=45871.5/2=22936 //需要计数22936个,计数范围为0~(22936-1),所以time_end=22935 always@(tone)begin case(tone) 5'd1: time_end= 16'd22935; //L1, 5'd2: time_end= 16'd20428; //L2, 5'd3: time_end= 16'd18203; //L3, 5'd4: time_end= 16'd17181; //L4, 5'd5: time_end= 16'd15305; //L5, 5'd6: time_end= 16'd13635; //L6, 5'd7: time_end= 16'd12147; //L7, 5'd8: time_end= 16'd11464; //M1, 5'd9: time_end= 16'd10215; //M2, 5'd10: time_end= 16'd9100; //M3, 5'd11: time_end= 16'd8589; //M4, 5'd12: time_end= 16'd7652; //M5, 5'd13: time_end= 16'd6817; //M6, 5'd14: time_end= 16'd6073; //M7, 5'd15: time_end= 16'd5740; //H1, 5'd16: time_end= 16'd5107; //H2, 5'd17: time_end= 16'd4549; //H3, 5'd18: time_end= 16'd4294; //H4, 5'd19: time_end= 16'd3825; //H5, 5'd20: time_end= 16'd3408; //H6, 5'd21: time_end= 16'd3036; //H7, default:time_end= 16'd65535; endcaseendreg[17:0]time_cnt;//当蜂鸣器使能时,计数器按照计数终值(分频系数)计数 always@(posedgeclk_inornegedgerst_n_in)begin if(!rst_n_in)begin time_cnt<=1'b0; endelseif(!tone_en)begin time_cnt<=1'b0; endelseif(time_cnt>=time_end)begin time_cnt<=1'b0; endelsebegin time_cnt<=time_cnt+1'b1; endend//根据计数器的周期,翻转蜂鸣器控制信号 always@(posedgeclk_inornegedgerst_n_in)begin if(!rst_n_in)begin piano_out<=1'b0; endelseif(time_cnt==time_end)begin piano_out<=~piano_out; //蜂鸣器控制输出翻转,两次翻转为1Hz endelsebegin piano_out<=piano_out; end end endmodule

小结

本节主要为大家讲解了蜂鸣器的不同类型及无源蜂鸣器的驱动原理,需要大家掌握的同时自己创建工程,通过整个设计流程,生成FPGA配置文件加载测试。