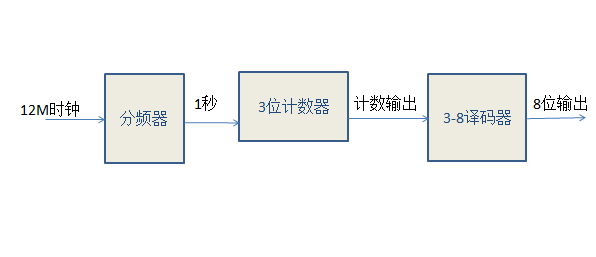

在时钟分频实验中我们练习了如何处理时钟,接下来我们要学习如何利用时钟来完成时序逻辑。硬件说明流水灯实现是很常见的一个实验,虽然逻辑比较简单,但是里面也包含了实现时序逻辑的基本思想。要用FPGA实现流水

Altera MAX10: LED流水灯

在时钟分频实验中我们练习了如何处理时钟,接下来我们要学习如何利用时钟来完成时序逻辑。====硬件说明====流水灯实现是很常见的一个实验,虽然逻辑比较简单,但是里面也包含了实现时序逻辑的基本思想。要用

Lattice MXO2: 时钟分频

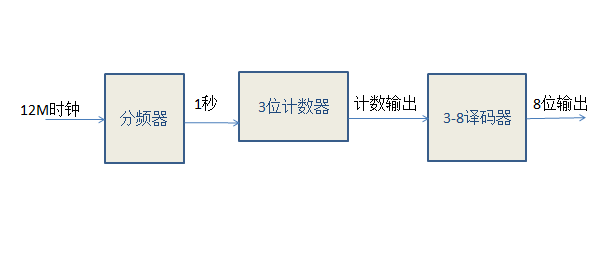

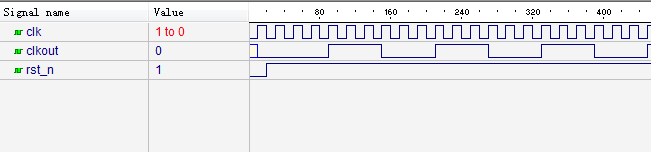

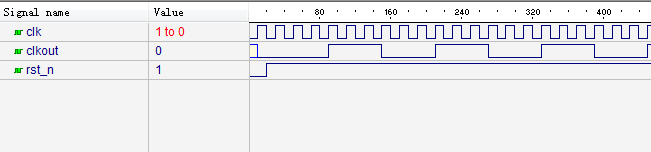

时钟分频在之前的实验中我们已经熟悉了小脚丫的各种外设,掌握了verilog的组合逻辑设计,接下来我们将学习时序逻辑的设计。硬件说明时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频

Altera MAX10: 时钟分频

时钟分频在之前的实验中我们已经熟悉了小脚丫的各种外设,掌握了verilog的组合逻辑设计,接下来我们将学习时序逻辑的设计。====硬件说明====时钟信号的处理是FPGA的特色之一,因此分频器也是FP

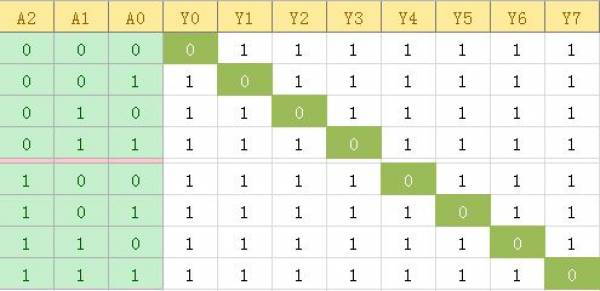

Altera MAX10: 3-8译码器

在这个实验里我们将学习如何用Verilog来实现组合逻辑。====硬件说明====组合逻辑电路是数字电路的重要部分,电路的输出只与输入的当前状态相关的逻辑电路,常见的有选择器、比较器、译码器、编码器、