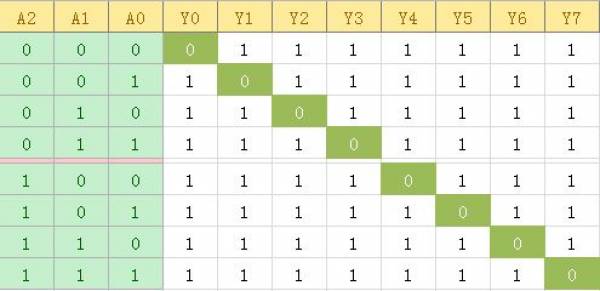

在这个实验里我们将学习如何用Verilog来实现组合逻辑。硬件说明组合逻辑电路是数字电路的重要部分,电路的输出只与输入的当前状态相关的逻辑电路,常见的有选择器、比较器、译码器、编码器、编码转换等等。在

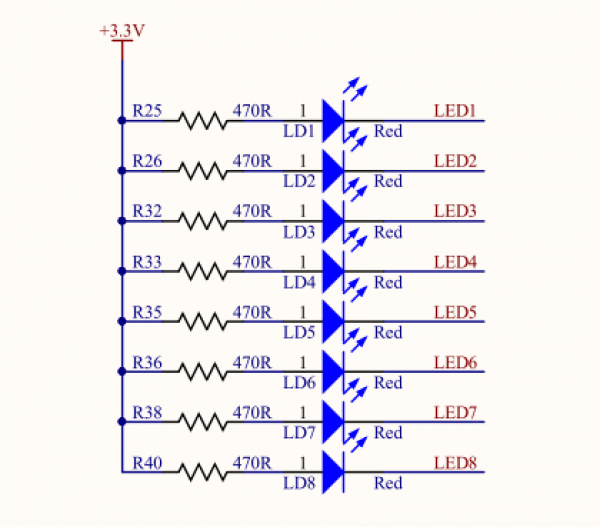

FPGA学习:点亮LED

恭喜你拿到我们的小脚丫开发板,在这个系列教程里你将更深入学习FPGA的设计同时更深入了解我们的小脚丫。如果你还没有开始使用小脚丫,也可以从这里一步一步开始你的可编程逻辑学习。请先到云盘准备好软硬件文档

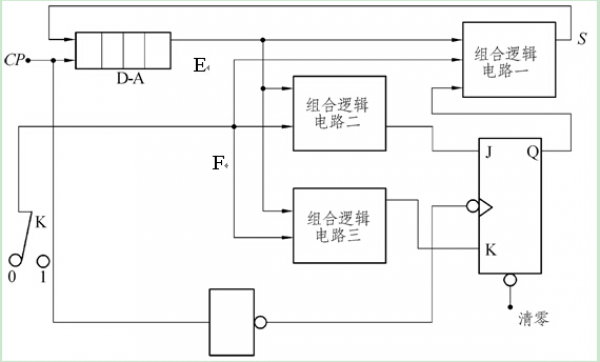

实验22 4位串行累加器

实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验了解累加器的意义及原理方法(3)掌握使用Verilog HDL语言基于FPGA实现累加器的原理及实现

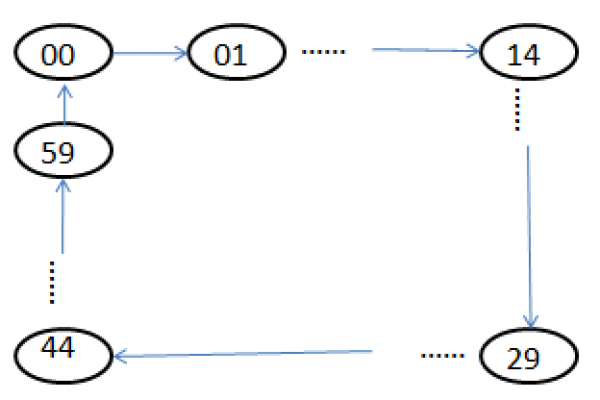

实验18:秒表计数器

实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握计数器原理;(3)掌握用Verilog HDL数据流和行为级描述寄存器单元的方法。实验任务

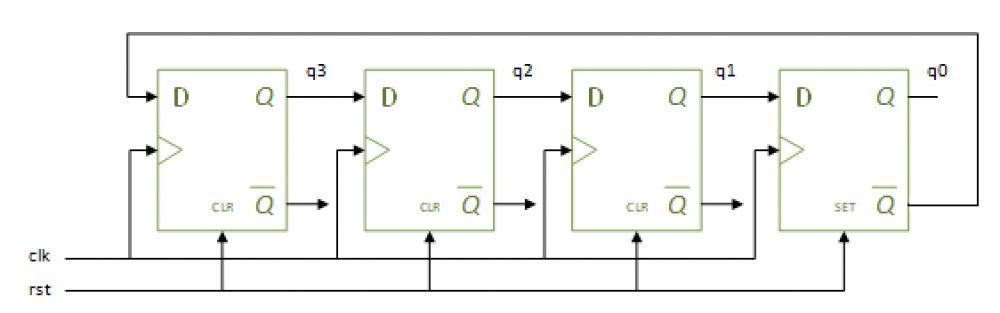

实验16:扭环形计数器

实验目的(1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;(2)通过实验理解和掌握扭环形计数器原理;(3)学习用Verilog HDL行为级描述时序逻辑电路。实验任务设计一